# **KINTSUGI**

# Identifying & addressing challenges in embedded binary security

JOS WETZELS

Supervisors: Prof. dr. Sandro Etalle Ali Abbasi, MSc.

Department of Mathematics and Computer Science Eindhoven University of Technology (TU/e)

June 2017

Kintsugi ("golden joinery"), is the Japanese art of repairing broken pottery with lacquer dusted or mixed with powdered gold, silver, or platinum. As a philosophy, it treats breakage and repair as part of the history of an object, rather than something to disguise.

**—**[254]

#### **ABSTRACT**

Embedded systems are found everywhere from consumer electronics to critical infrastructure. And with the growth of the Internet of Things (IoT), these systems are increasingly interconnected. As a result, embedded security is an area of growing concern. Yet a stream of offensive security research, as well as real-world incidents, continues to demonstrate how vulnerable embedded systems actually are.

This thesis focuses on binary security, the exploitation and mitigation of memory corruption vulnerabilities. We look at the state of embedded binary security by means of quantitative and qualitative analysis and identify several gap areas and show embedded binary security to lag behind the general purpose world significantly.

We then describe the challenges and limitations faced by embedded exploit mitigations and identify a clear open problem area that warrants attention: deeply embedded systems. Next, we outline the criteria for a deeply embedded exploit mitigation baseline. Finally, as a first step to addressing this problem area, we designed, implemented and evaluated  $\mu Armor$ : an exploit mitigation baseline for deeply embedded systems.

When you want to know how things really work, study them when they're coming apart.

- William Gibson

#### **ACKNOWLEDGEMENTS**

First of all, I would like to thank my supervisors, Prof. dr. Sandro Etalle and Ali Abbasi, MSc., for their assistance and support throughout the process of researching and writing this thesis. Sandro's guidance helped me structure the rather voluminous body of research produced by this thesis while Ali's continuous feedback and brainstorming helped this work achieve its current depth.

Secondly, I am grateful to my family, without whom none of this would have been possible, for their unconditional love and support.

Finally, I am thankful to my friends for their moral support and to the many people from the information security field and the outer reaches of the internet who, over the years, have continued to inspire me.

Jos Wetzels Eindhoven University of Technology (TU/e) June 2017

# CONTENTS

| Ι  | EM                | IBEDDED BINARY SECURITY                           | 1  |

|----|-------------------|---------------------------------------------------|----|

| 1  | INT               | RODUCTION                                         | 3  |

|    | Problem Statement | 3                                                 |    |

|    | 1.2               | Research Goal & Questions                         | 4  |

|    | 1.3               | Contributions                                     | 4  |

|    | 1.4               | Outline                                           | 5  |

| 2  | BAC               | CKGROUND                                          | 7  |

|    | 2.1               | Basic Embedded Concepts                           | 7  |

|    | 2.2               | Embedded Security Threat Landscape                | 11 |

|    | 2.3               | Embedded Patching Issues                          | 14 |

|    | 2.4               | Memory Corruption Vulnerabilities                 | 17 |

|    |                   | 2.4.1 Language Safety                             | 18 |

|    |                   | 2.4.2 'Weird Machines' & Exploitation             | 19 |

|    | 2.5               | Exploit Mitigations                               | 20 |

| 3  | EMI               | BEDDED EXPLOIT MITIGATION BASELINE                | 25 |

|    | 3.1               | Establishing a Minimum Baseline                   | 25 |

|    | 3.2               | Baseline Mitigations In-Depth                     | 26 |

|    |                   | 3.2.1 Executable Space Protection (ESP)           | 26 |

|    |                   | 3.2.2 Address Space Layout Randomization (ASLR) . | 30 |

|    |                   | 3.2.3 Stack Canaries                              | 34 |

|    | 3.3               | Exploit Mitigation Dependencies                   | 36 |

|    |                   | 3.3.1 ESP Dependencies                            | 36 |

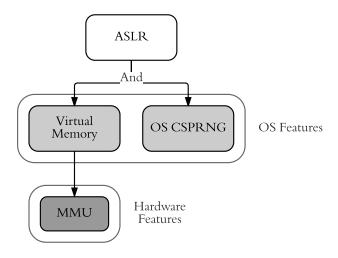

|    |                   | 3.3.2 ASLR Dependencies                           | 38 |

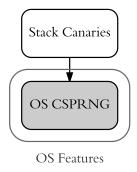

|    |                   | 3.3.3 Stack Canary Dependencies                   | 39 |

| II | AN                | NALYSIS OF EMBEDDED EXPLOIT MITIGATIONS           | 41 |

| 4  | QUA               | ANTITATIVE ANALYSIS                               | 43 |

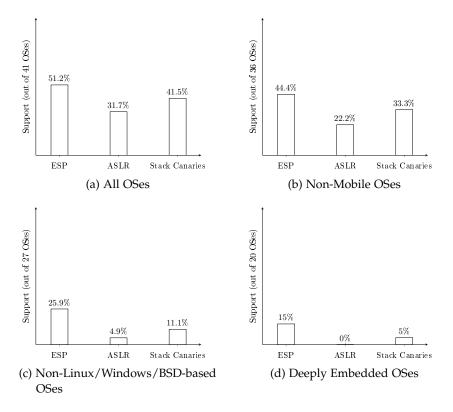

|    | 4.1               | Embedded OS mitigation & dependency support       | 43 |

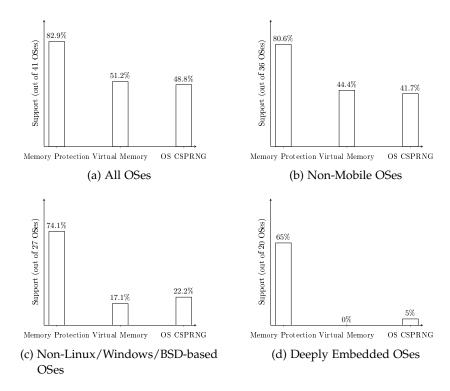

|    | 4.2               | Embedded hardware feature support                 | 44 |

|    | 4.3               | Conclusions                                       | 48 |

| 5  | QUA               | ALITATIVE ANALYSIS                                | 53 |

|    | 5.1               | QNX                                               | 53 |

|    |                   | 5.1.1 Security History                            | 55 |

|    |                   | 5.1.2 QNX ESP                                     | 55 |

|    |                   | 5.1.3 QNX ASLR                                    | 56 |

|    |                   | 5.1.4 QNX Stack Canaries                          | 64 |

|    |                   | 5.1.5 QNX OS CSPRNG                               | 67 |

|    | 5.2               | RedactedOS                                        | 73 |

|    |                   | 5.2.1 RedactedOS OS CSPRNG                        | 74 |

|    | 5.3               | Zephyr                                            | 75 |

|    |                   | 5.3.1 Zephyr Stack Canaries                       | 77 |

|    | 5.4               | Conclusions                                       | 80 |

| 6   | FMB  | BEDDED CHALLENGES                                   | 83         |

|-----|------|-----------------------------------------------------|------------|

| Ü   | 6.1  | Development Practices & Cost Sensitivity            | 83         |

|     | 6.2  | Resource Constraints                                | 84         |

|     | 6.3  | Safety, Reliability & Real-Time Requirements        | 85         |

|     | _    | Hardware & OS Limitations                           |            |

|     | 6.4  |                                                     | 87         |

|     |      | 6.4.1 MPUs, MMUs & Hardware ESP                     | 87         |

|     |      | 6.4.2 Virtual Memory                                | 88         |

|     |      | 6.4.3 Advanced Processor Features                   | 88         |

|     | _    | 6.4.4 OS CSPRNGs                                    | 89         |

|     | 6.5  | Open Problems                                       | 91         |

|     |      | 6.5.1 Deeply Embedded Exploit Mitigation Criteria . | 92         |

|     |      | 6.5.2 OS CSPRNG Design for Deeply Embedded Sys-     |            |

|     |      | tems                                                | 93         |

| III | μΑ   | RMOR DESIGN, IMPLEMENTATION & EVALUATION            | 95         |

| 7   | μAR  | RMOR DESIGN                                         | 97         |

|     | 7.1  | Representative Platform                             | 97         |

|     | 7.2  | Attacker Model                                      | 98         |

|     | 7.3  | High-Level Design                                   | 98         |

|     | 7.4  | μESP Design                                         | 99         |

|     | 7.5  | μScramble Design                                    | 101        |

|     | 7.6  | μSSP Design                                         | 105        |

|     | 7.7  | μRNG Design                                         | 107        |

| 8   | μAR  | RMOR IMPLEMENTATION                                 | 113        |

|     | 8.1  | μESP Implementation                                 | 113        |

|     | 8.2  | μScramble Implementation                            | 116        |

|     | 8.3  | μSSP Implementation                                 | 118        |

|     | 8.4  | μRNG Implementation                                 | 119        |

| 9   | •    | RMOR EVALUATION & LIMITATIONS                       | 121        |

| פ   | 9.1  | Real-Time Compatibility & Safety Issues             | 121        |

|     | 9.2  | Overhead Evaluation                                 | 121        |

|     |      | Security Evaluation                                 |            |

|     | 9.3  | 9.3.1 µESP Security                                 | 129<br>129 |

|     |      | 9.3.2 µScramble Security                            | 129        |

|     |      | 9.3.3 µSSP Security                                 |            |

|     |      | 9.3.4 µRNG Security                                 | 133        |

|     | 0.4  | Limitations                                         | 134        |

|     | 9.4  | Limitations                                         | 136        |

| IV  | CO   | NCLUSION                                            | 137        |

| 10  | REL  | ATED WORK                                           | 139        |

|     |      | Embedded Mitigation Support & Quality               | 139        |

|     | 10.2 | Embedded Mitigation Design                          | 139        |

| 11  | DISC | CUSSION, CONCLUSIONS & FUTURE WORK                  | 145        |

|     | 11.1 | Discussion                                          | 145        |

|     | 11.2 | Conclusions                                         | 147        |

|     | 11.3 | Future Work                                         | 1/18       |

| V  | APPENDIX           | 151 |

|----|--------------------|-----|

| A  | SUPPLEMENTARY DATA | 153 |

| ΒI | BLIOGRAPHY         | 165 |

CONTENTS

xi

# LIST OF FIGURES

| Figure 1  | Library-Based Operating System Example 11        |  |  |

|-----------|--------------------------------------------------|--|--|

| Figure 2  | Memory corruption exploitation flowchart demon-  |  |  |

| _         | strating mitigations at different stages based   |  |  |

|           | on [390]                                         |  |  |

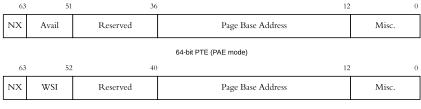

| Figure 3  | x86 Page Table Entry (PTE) with NX bit 29        |  |  |

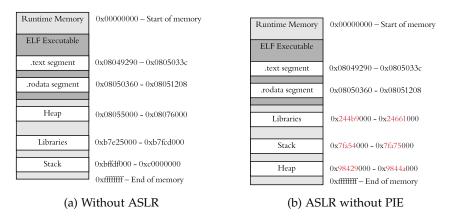

| Figure 4  | Address Space Layout Randomization (ASLR) [22] 3 |  |  |

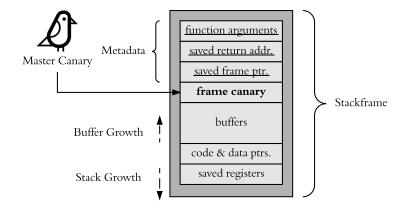

| Figure 5  | Stack Canary Example 34                          |  |  |

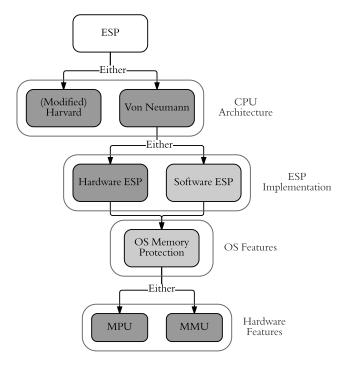

| Figure 6  | ESP Dependencies                                 |  |  |

| Figure 7  | ASLR Dependencies                                |  |  |

| Figure 8  | Stack Canary Dependencies 39                     |  |  |

| Figure 9  | Embedded OS Exploit Mitigation Support 44        |  |  |

| Figure 10 | Embedded OS exploit mitigation dependency        |  |  |

|           | support                                          |  |  |

| Figure 11 | Core Family dependency support 48                |  |  |

| Figure 12 | QNX Architecture [233] 54                        |  |  |

| Figure 13 | QNX Private Virtual Memory [220] 54              |  |  |

| Figure 14 | QNX Memory Layout (x86) 57                       |  |  |

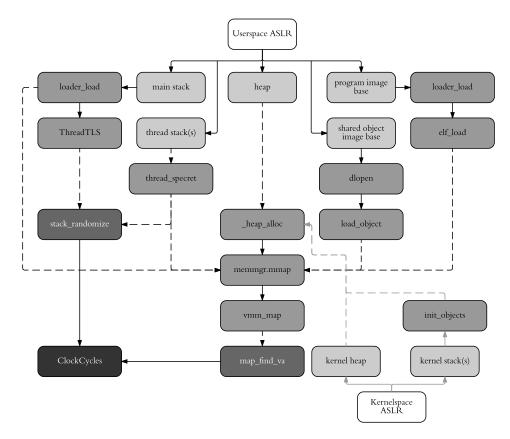

| Figure 15 | QNX ASLR Memory Object Graph 60                  |  |  |

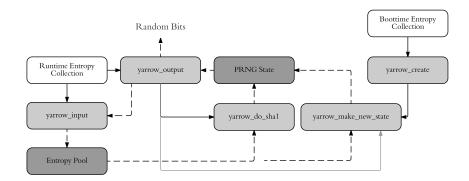

| Figure 16 | Simplified QNX Yarrow 6.6 Design 68              |  |  |

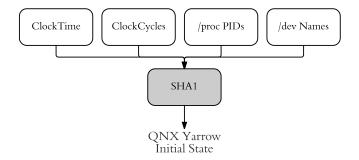

| Figure 17 | QNX Yarrow Boottime Entropy Collection 70        |  |  |

| Figure 18 | QNX Yarrow Restart Boottime Entropy Visual-      |  |  |

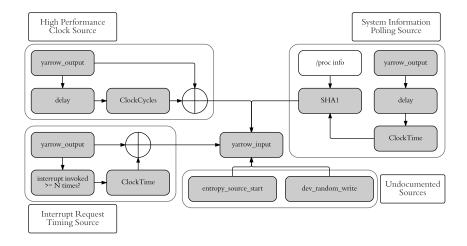

|           | ization [43]                                     |  |  |

| Figure 19 | QNX Yarrow Runtime Entropy Collection 73         |  |  |

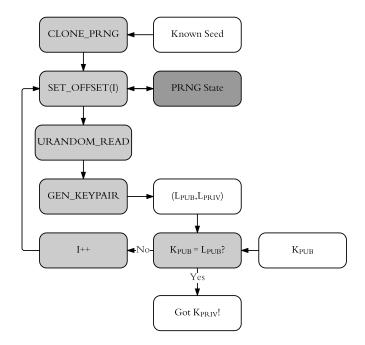

| Figure 20 | RedactedOS PRNG Known Seed Attack 76             |  |  |

| Figure 21 | Zephyr Architecture [186]                        |  |  |

| Figure 22 | μArmor High-Level Design as a subgraph of        |  |  |

|           | Figure 2                                         |  |  |

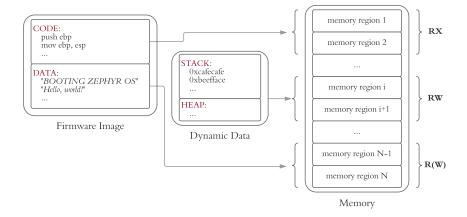

| Figure 23 | μESP Design                                      |  |  |

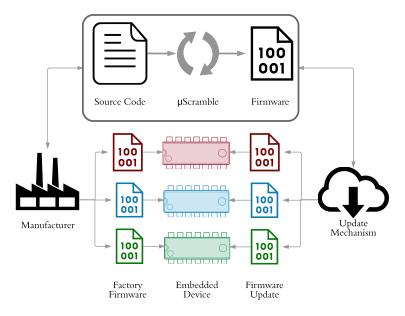

| Figure 24 | μArmor Firmware Distribution Process 101         |  |  |

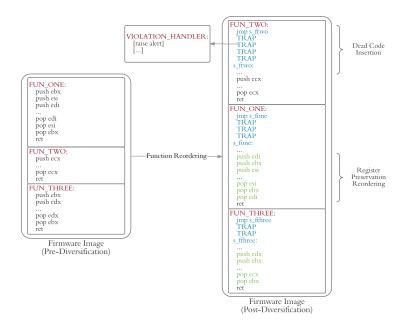

| Figure 25 | μScramble Firmware Diversification 102           |  |  |

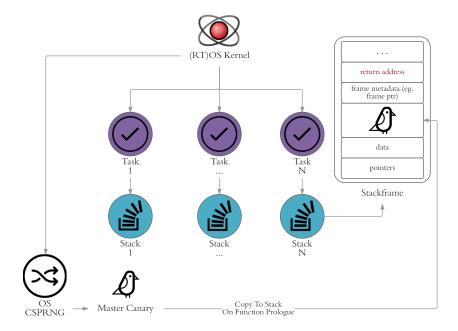

| Figure 26 | μSSP Design                                      |  |  |

| Figure 27 | μRNG Design                                      |  |  |

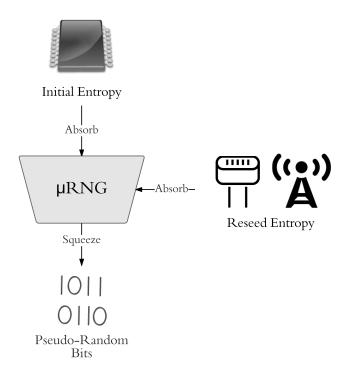

| Figure 28 | μRNG Reseed Control 108                          |  |  |

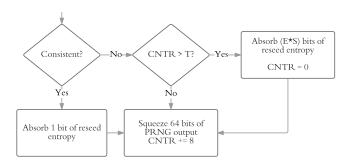

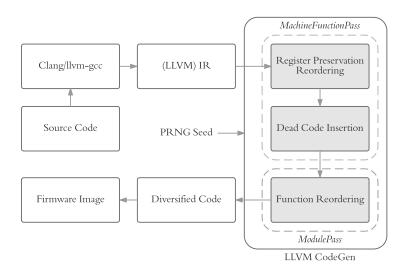

| Figure 20 | uscramble LLVM Implementation 117                |  |  |

# LIST OF TABLES

| Table 1  | Embedded OS exploit mitigation adoption 45                  |

|----------|-------------------------------------------------------------|

| Table 2  | Embedded OS exploit mitigation dependency                   |

|          | support                                                     |

| Table 3  | Core Family dependency support 49                           |

| Table 4  | Core Family dependency support 50                           |

| Table 5  | Core Family dependency support 51                           |

| Table 6  | QNX Hardware ESP Support                                    |

| Table 7  | QNX Address Boundaries 57                                   |

| Table 8  | QNX Default Libc Load Addresses 58                          |

| Table 9  | QNX ASLR Memory Object Randomization Sup-                   |

|          | port                                                        |

| Table 10 | QNX ClockCycles Implementations 61                          |

| Table 11 | QNX ASLR Userspace Memory Object Min En-                    |

|          | tropy 62                                                    |

| Table 12 | QNX Stack Canary Min Entropy 66                             |

| Table 13 | Qualitative Exploit Mitigation Analysis Overview 82         |

| Table 14 | μESP Memory Permission Policies 114                         |

| Table 15 | TI LM3S6965 MPU μESP Settings, execute-from-                |

|          | flash                                                       |

| Table 16 | TI LM3S6965 MPU μESP Settings, execute-from-                |

|          | <i>RAM</i>                                                  |

| Table 17 | μESP Overhead Evaluation                                    |

| Table 18 | μSSP Overhead Evaluation                                    |

| Table 19 | μRNG Overhead Evaluation 124                                |

| Table 20 | μScramble Overhead wrt. Application 125                     |

| Table 21 | μScramble Overhead wrt. Application 126                     |

| Table 22 | μScramble Overhead wrt. Resources 127                       |

| Table 23 | μScramble Overhead wrt. Resources 128                       |

| Table 24 | μRNG Resource Consumption Comparison 129                    |

| Table 25 | μScramble Coverage Analysis 131                             |

| Table 26 | μScramble Coverage Analysis                                 |

| Table 27 | TRNG support among Zephyr 1.8 supported                     |

| -        | boards                                                      |

| Table 28 | Popular Embedded Development Board Resources <sub>155</sub> |

| Table 29 | Benchmarks & Applications selected from TACLeBench          |

|          | Suite [357]                                                 |

| Table 30 | Benchmarks & Applications selected from TACLeBench          |

|          | Suite [257]                                                 |

# LISTINGS

| Listing 1  | μESP MPU Setup Pseudo-Code 114                   |

|------------|--------------------------------------------------|

| Listing 2  | QNX vmm_mmap Routine                             |

| Listing 3  | QNX map_create Routine                           |

| Listing 4  | QNX map_find_va Routine 159                      |

| Listing 5  | QNX stack_randomize Routine 160                  |

| Listing 6  | QNX Stack Canary Failure Handler (User-Space)160 |

| Listing 7  | QNX Stack Canary Generation Handler 161          |

| Listing 8  | QNX Stack Canary Failure Handler (Kernel-        |

|            | Space)                                           |

| Listing 9  | QNX Yarrow HPC Entropy Collection Snippet 161    |

| Listing 10 | QNX 6.6.0 yarrow_do_sha1 function 162            |

| Listing 11 | QNX 6.6.0 yarrow_make_new_state function . 162   |

| Listing 12 | Zephyr Stack Canary Generation Handler 163       |

| Listing 13 | Zephyr Timer Random Number Generator 163         |

#### **ACRONYMS**

GP General Purpose

CPS Cyber-Physical Systems

MCU Microcontroller Unit

SoC System-on-a-Chip

RTOS Real-Time Operating System

MMU Memory Management Unit

MPU Memory Protection Unit

OEM Original Equipment Manufacturer

ODM Original Device Manufacturer

ICS Industrial Control System

ESP Executable Space Protection

ASLR Address Space Layout Randomization

TRNG True Random Number Generator

(CS)PRNG (Cryptographically Secure) Pseudorandom Number Generator

# Part I EMBEDDED BINARY SECURITY

INTRODUCTION

#### 1.1 PROBLEM STATEMENT

Embedded systems are everywhere. From consumer electronics, networking equipment and critical infrastructure to vehicles, airplanes, military hardware and medical equipment: they underpin the technological fabric of society [88, 237, 240–242]. Over the years embedded systems have become increasingly interconnected [13], a trend that is exacerbated by the rise of the so-called '*Internet of Things (IoT)*' which has been projected to grow from roughly 5 billion [102] deployed devices in 2015 to anywhere between 20 [102] and 50 billion [139] in 2020.

Contrary to its popular image, the IoT is not just limited to *smart home* and *wearable* consumer electronics. While most people are familiar with such gadgets, the real drive behind IoT growth comes from enterprise applications [121, 245]. Some examples are asset tracking, production line monitoring and automation in the *industrial IoT* [431], *smart grid* [335] and smart meter deployment in the energy sector and streamlining of lighting, parking, surveillance and public infrastructure optimization in *smart cities* [358].

The growing interconnectedness of embedded systems has made security an increasingly important concern [13, 101, 202, 203]. Not only because the systems themselves are interesting targets for attackers but also because many of these systems weren't designed to be connected to networks in the first place. And with the growth of the IoT these concerns are set to spread to many different sectors. Such concerns are not merely theoretical as real-world incidents involving embedded systems have shown. Nor are they limited to one particular group of systems or industry vertical: incidents occur everywhere from the infamous Stuxnet attack against nuclear facilities in Iran [413], recent attacks against Ukrainian power grid [178, 278, 323] and the hacking of smart TVs by intelligence agencies [70] to the formation of massive botnets consisting of compromised IoT devices [145]. And with new attacks on embedded systems in everything from cars [36, 308] to medical equipment [189, 451] being demonstrated, the importance of embedded security is virtually selfevident.

Yet embedded systems security is generally seen as lagging behind what we've come to expect of our general purpose (eg. desktop and server) systems [202, 203, 205, 421, 422]. Embedded 'binary security' in particular is an area where exploitation of vulnerabilities is significantly easier than on general purpose systems. This is exemplified by a 2016 incident where a previously unknown group calling themselves the "Shadow Brokers" released a cache of exploits which they claimed belonged to the supposedly state-sponsored "Equation Group" [78] threat actor. Among this cache were a set of exploits for high-end firewall equipment of multiple manufacturers [5], none of which had to bypass any exploit mitigations.

However, despite the general perception of embedded systems binary security as lagging, there is a lack of quantitative and qualitative research providing insight into the current state-of-the-art and its gap areas.

#### 1.2 RESEARCH GOAL & QUESTIONS

**Research Goal**: The goal of this work is to identify the state-of-the-art in embedded operating system binary security and contribute to improve the security of embedded systems, in particular against memory corruption attacks.

The following **research questions** have to be answered in order to achieve the stated research goal:

- **RQ-1**: What would a minimum exploit mitigation baseline for embedded systems look like?

- **RQ-2**: What is the current state-of-the-art in embedded operating system exploit mitigations in terms of adoption, dependency support and implementation quality?

- **RQ-3**: What are the gap areas and open problems within the current state-of-the-art and what are the challenges underlying them?

- **RQ-4**: Given the clearest gap area identified, what would an effective solution look like and what criteria should it meet?

# 1.3 CONTRIBUTIONS

This work makes the following, to the best of our knowledge, novel contributions:

We establish a minimum exploit mitigation baseline for embedded systems and outline its security criteria and hardware- and software dependencies.

- 2. We perform the first *quantitative analysis* of the state of embedded exploit mitigation adoption and support for software- and hardware dependencies. This analysis shows that embedded systems lag behind general purpose ones significantly in this regard.

- 3. We perform the first *qualitative analysis* of the exploit mitigations and secure random number generators of three embedded operating systems: QNX, RedactedOS and Zephyr. This analysis shows their implementations to be flawed in various ways. We responsibly disclosed the vulnerabilities we uncovered in the course of this analysis to the vendors in question and collaborated in drafting fixes.

- 4. In order to explain the results of our analyses, we provide the first systematic identification of the challenges embedded exploit mitigation adoption efforts face. We then identify two major open problems and outline the criteria for their solutions.

- 5. We propose, implement and evaluate μArmor: the first exploit mitigation baseline design for constrained *deeply embedded systems*, thereby addressing the identified open problems.

#### 1.4 OUTLINE

**Part i** provides a background on embedded systems and binary security in Chapter 2 and presents an embedded exploit mitigation baseline in Chapter 3. **Part ii** presents our analyses of the state of embedded exploit mitigations in the form of a quantitative analysis in Chapter 4, a qualitative analysis in Chapter 5 and a discussion of challenges, open problems and criteria in Chapter 6. **Part iii** presents our work on μArmor and discusses its design in Chapter 7, its implementation in Chapter 8 and its evaluation in Chapter 9. **Part iv** contains an overview of related work in Chapter 10 and discussion, conclusions and future work in Chapter 11. Finally, **Appendix A** contains supplementary data such as tables, benchmarking information and code snippets.

2

#### 2.1 BASIC EMBEDDED CONCEPTS

The term 'embedded systems' covers a wide range of devices used for a myriad of different purposes. They can be as simple as a single pressure sensor node or a digital alarm clock or as complicated as flight management systems, medical imaging equipment or military weapons systems.

### Embedded & General-Purpose Systems

An **embedded system** is "a combination of computer hardware and software, and perhaps additional mechanical or other parts, designed to perform a dedicated function. In some cases, embedded systems are part of a larger system or product, as in the case of an antilock braking system in a car. Contrast with general-purpose computer" [402].

This is contrasted with a **general purpose (GP) system** which is "a combination of computer hardware and software that serves as a general-purpose computing platform. PCs, Macs, and Unix workstations are the most popular modern examples" [402].

Due to the incredible diversity of embedded systems, it is impossible to say what a 'typical' embedded system looks like. They can range from high-end systems with a user interface to constrained deeply embedded systems engaging only in machine-to-machine (M2M) communications as part of a Cyber-Physical System (CPS).

#### Deeply Embedded & Cyber-Physical Systems (CPS)

Deeply embedded systems [423] are those systems on the most highly integrated and constrained end of the embedded spectrum and serve dedicated, single purposes (eg. collecting sensor data, basic processing or automation, etc.). These systems tend to use resource-constrained *microcontrollers* which allow for low production cost. Deeply embedded system often lack user interfaces and tend to be either *bare metal* or run extremely minimal operating systems. They are generally not (dynamically) programmable once the program logic has been burned into ROM and require either device programmers or bootloader-assisted firmware reflashing.

Cyber-Physical Systems (CPS) are a "class of engineered systems that offer close interaction between cyber and physical components" [442] characterized by deep integration between physical and software components that are "typically designed as a network of interacting elements with physical input and output instead of as standalone devices" [131]. Examples of CPS include automotive, avionics and aerospace systems, industrial control systems and 'smart grids', robotics systems, medical monitoring and robotic surgery systems, military and defense systems, etc.

As a result, embedded systems hardware can range from simple 8-bit *microcontrollers* to a *System-on-a-Chip* (*SoC*) outfitted with a multicore 32- or 64-bit microprocessor.

# Microprocessors, Microcontrollers (MCUs) and System-on-a-Chip (SoC)

**Microprocessors** incorporate CPU functionality on a single integrated circuit (IC) (or at most a small number of them), reducing the cost of processing power. **Microcontroller Units** (**MCUs**) essentially integrate a CPU along with memory and peripherals on a single IC. This high degree of integration allows for size and cost reductions that make MCUs ideally suited for embedded deployment.

The term **System-on-a-Chip (SoC)** refers to systems with a high degree of integration of all components of a computer or other electronic system. The difference with MCUs is often one of degree, with MCUs generally being actual single-chip systems while the term SoC is often used as hyperbole indicating a high degree of but not completely single-chip integration. Typical SoCs consist of an MCU, microprocessor or digital signal processor (DSP) core and memory, peripherals, external interfaces (eg. USB, Ethernet, etc.) or power management functionality.

Some embedded systems run an operating system while others are only outfitted with a piece of *bare metal* (ie. OS-less) application firmware. Embedded operating systems themselves come in many different flavors too, from variants of popular general-purpose OSes to tiny *real-time operating systems* (*RTOS*) and from *monolithic* kernel architectures to *microkernel* designs.

#### Real-Time Operating System (RTOS)

Real-Time Operating Systems (RTOS) are "designed specifically for use in real-time systems" [402], the latter being "any computer system, embedded or otherwise, that has timeliness requirements" [402]. That is to say: those systems which must be able to guarantee a response within specified time constraints with varying degrees of 'hardness'. The 'harder' these constraints, the more serious missing a deadline is considered. As such real-time systems are more about deterministic and predictable response times than fast ones [344]. Real-time requirements are particularly important in safety-critical applications such as flight control software, automotive brake controls or industrial manufacturing processes.

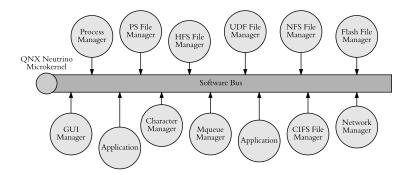

#### Monolithic & Microkernel Architectures

As opposed to **monolithic kernels** where "all functionality provided by the OS is realized within the kernel itself" [344], a micro**kernel** "reduces the services provided by the kernel dramatically by putting all services, which are not essentially necessary for the microkernel, into user space as isolated processes. (...) The service processes typically behave like servers of the client-server model. To use such a service an application needs to send a message with a service request to the service which receives the request, completes the request and sends back a response message to the client application. (...) The big advantage of microkernels against monolithic kernels is the clear separation of services from the kernel itself making the kernel a very small piece of software that provides a better fault isolation and can be maintained more easily than a monolithic kernel. The fault isolation prevents crashing the whole system. (...) The price we have to pay for the better structuring and fault isolation is that we get a high amount of interprocess communication through message passing and a high amount of context switching" [344].

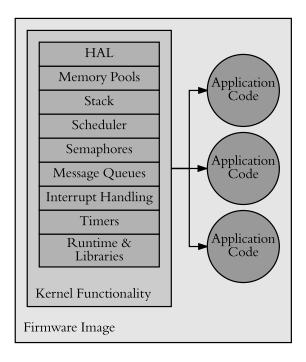

While the high-end embedded operating systems found in smart-phones or certain networking equipment are often based on Linux-, BSD- or even Windows and as such are familiar to people used to the general purpose world, the *library-based operating systems* aimed at the low-end of the embedded spectrum are quite different as illustrated in Figure 1.

#### Library-Based Operating Systems

Library-based operating systems implement the OS as a collection of libraries which are linked together with the application code into "one single executable which is executed in one single address space. Therefore no loader is required to dynamically load applications at run-time, by this minimizing the operating system code. Another advantage of a library-based RTOS and the execution in a single common address space is that system calls can be simply implemented as function calls. Thus no context-switches are required when calling an operating system function. This is often more efficient and less time consuming as a full context switch with address space changes when having an RTOS implemented as a kernel in a separated address space" [344]. A disadvantage of library-based OSes is the lack of safety and security that comes with running all application code and kernel code in the same address space as a result of the lack of memory separation.

Figure 1: Library-Based Operating System Example

#### 2.2 EMBEDDED SECURITY THREAT LANDSCAPE

The world of embedded systems is incredibly diverse and spans many industry verticals. As such, rather than establishing a single comprehensive overview of the threat landscape we will outline some of the key differences between the embedded and general purpose worlds:

1. **Security Attention**: Security has been a serious concern in a minority of industries dealing with embedded systems (eg. payment cards, video game consoles, PayTV solutions, etc.), but this has usually been the result of the fact that security issues in such devices directly threaten corporate revenue streams, intellectual property or the core business model. Since this is not the case for most other industries, attention to the security of embedded systems has continued to structurally lag behind what we've come to expect of general purpose systems. A recent joint report by the *European Union Agency for Network and Information Security (ENISA)* and semiconductor manufacturers *Infineon, NXP* and *STMicroelectronics* speaks of a "market failure for cybersecurity and privacy" [56], a sentiment which is echoed by Bruce Schneier [202].

The ENISA report observes that there is "no basic level, no level zero defined for the security and privacy of connected and smart devices" [56], a troubling observation considering the increasing

connectivity and corresponding exposure of embedded systems [13]. This is compounded by a common 'confusion' between *safety* and *security* requirements. While the prior is a core requirement of many embedded systems and enforced by regulations and certifications, it does not cover the latter which deals with *actively malicious* subversion of a system. This was illustrated in one recent study [88] where 22% of the surveyed designers of Internet-connected safety-critical systems indicated security was not a design requirement.

2. **Security Concerns**: The security concerns of embedded systems are often quite different from those in the general purpose world as well. A 2017 embedded safety & security study [88] found the three primary security concerns to be *product tampering*, theft of data and theft of intellectual property, all of which relate more to the company which designed the product than to the users. This is despite the fact that security threats to embedded systems are growing more serious with the involvement of government-sponsored hacking [17] rather than the traditionally more restricted attackers such as pirates or competitors.

When attacking desktop or server systems, attackers often attempt to obtain users' documents or sensitive financial information. In embedded systems, however, attacker goals tend to be more device-specific because of their single-purpose nature. An attacker might try to sabotage a *cyber-physical system* [281] (causing electrical blackouts or car crashes), tamper with measurements (smart meter fraud), bypass authentication procedures (building access control) or device restrictions (pirated entertainment media), conduct surveillance (network equipment or smart home hacking) or steal intellectual property (code extraction and reverse engineering). Sometimes the attacker goal is only indirectly related to the embedded system in question, such as when connected embedded systems are used to pivot into corporate networks [64, 125] or launch *Distributed Denial-of-Service* attacks [126].

Such attacks can involve anything from flipping a few bits somewhere in memory or extracting a single cryptographic key to obtaining full code execution; in some cases, attackers might have physical access to the device in question (especially when users themselves are potential adversaries). This opens up a wide range of attacks [8] ranging from abusing exposed debugging functionality [93] or side-channel and glitching attacks [80, 170] to more invasive attacks involving chip decapping and optical reverse-engineering [80, 236, 283]. A more exhaustive survey

of threats and concerns can be found in the ENISA "Hardware Threat Landscape and Good Practice Guide" [55].

3. Ecosystem Differences: Embedded 'ecosystems' are characterized by a number of particular challenges, addressed in Chapter 6, around development practices, resource constraints, system requirements and limitations that are very different from the general purpose world. With respect to security these ecosystem differences also translate to difficulties in patching (addressed in Section 2.3), host- and network-based intrusion detection [193, 205, 333, 395, 397, 433] and forensics [12, 119, 120, 427]. Finally, as observed in a recent Barr Group study [88], the sheer *diversity* of embedded systems in terms of hardware, software and applications prohibits the emergence of a one-size-fits-all security solution.

The embedded devices used in certain industries pose a bigger risk than those in others. Networked, safety-critical devices in particular pose a major risk and within that group a handful of systems is associated with more than two-thirds of the risk [88]: *medical devices, industrial control systems* and *automotive systems* followed by *consumer electronics* and *defense & aerospace systems*.

Below we present a brief overview of some of the practical attacks, not all of which are relevant to *embedded binary security*, that have been demonstrated to affect these systems in order to illustrate how serious the situation is. For a more exhaustive overview of the threats we refer to the work in [129, 281, 330, 449].

Medical: Medical devices are often intimately coupled to lethal risk but despite this practical attacks have been demonstrated on infusion pumps [82, 115, 189, 314], pacemakers and ICDs [320, 328], ECGs [424], surgical robots [451] and bionic arms [6]. While realworld incidents are rare, a recent ransomware attack ended up infecting a power injector [71] responsible for injecting contrast agent for CT and MRI scans.

**Industrial Control Systems (ICS)**: Interest in ICS security has skyrocketed in the wake of *Stuxnet* [413] with attacks being demonstrated on everything from PLCs [21], RTUs [287] and HMI [178] to DTM components [286] and rootkits [289, 393], worms [425] and ransomware [325] having been developed specifically for ICS devices. Meanwhile, recent real-world incidents targeting industrial control systems have caused blackouts on the Ukrainian power grid [178, 278, 323] and physically damaged a German steel mill [277].

**Automotive**: Modern automobiles are complicated networks of computer systems, essentially "a computer with four wheels and an engine" [203], with an ever-growing and highly vulnerable attack surface [100, 212, 330]. Attacks have been demonstrated on everything from the CAN bus and Engine Control Unit (ECU) [36, 62, 130, 301, 309–311, 379, 444], Anti-lock Braking System (ABS) [464], Tire Pressure Monitoring System (TPMS) [249, 366] or infotainment and telematics systems [308, 361, 385, 432] to Remote Keyless Entry (RKE) [251, 341] and Immobilizer [168, 169, 429, 443] systems.

**Smart Homes and Consumer IoT**: The rise of consumer-oriented IoT gadgets, particularly in the *smart home* sphere, is just a fragment of the total consumer electronics market but has seen a proliferation of so-called *'junk hacking'* [86, 150] targeting almost every type of device including smart home gadgets [318], alarm systems [34, 127, 468], locks and access control systems [27, 144, 191, 297, 477], surveillance cameras [44, 92, 438, 479], thermostats [349] and smart TVs [70, 400, 440].

Defense & Aerospace: 'Cybersecurity' in the context of military embedded systems has received increasingly more attention with the recognition of 'cyberspace' as a fifth domain of warfare. Given the overlap with more established military security concerns such as Electronic Warfare (EW) [87, 362] and Communications Security (COMSEC) the dividing line with 'cyber' becomes blurry. For obvious reasons, there is little detailed public research regarding attacks on military and aerospace systems but one related area that stands out for its accessibility to independent researchers is that of Unmanned Aerial Vehicle (UAV) / drone security. This is mainly due to the proliferation of and subsequent security research on commercial UAVs [32, 113, 196] but recent work has shown government UAVs, including those used by the military, are vulnerable as well [32, 166, 294, 382]. In addition, real-world incidents have taken place over the past decade involving signals interception [10, 114, 252] and hijacking [173] of military UAVs.

#### 2.3 EMBEDDED PATCHING ISSUES

When a vulnerability is discovered in a computer system a patch should be created and applied, ideally as soon as possible. In order to avoid making constant patch application the responsibility of users, many general purpose operating systems contain integrated functionality for secure and automated patch management. The embedded world is very different in this regard where many systems require manually applied updates or are unpatchable altogether and vendors sometimes don't even provide a patch in the first place. There are var-

ious reasons why embedded patch management is complicated [202, 423]:

1. Broken Patch Management: Effective patch management requires an infrastructure that ensures a patch gets securely from the party responsible for creating patches to all affected devices with minimal interaction. For embedded systems, the problem starts with fragmented responsibility. As discussed in more detail in Section 6.1, no single entity manages the entire software development lifecycle of an embedded product. As a result, it is not always clear who is responsible for creating a patch when a vulnerability is discovered nor are all parties equally incentivized to create one which leads to an absence of (timely) fixes for embedded vulnerabilities. Industrial control systems are illustrative of the latter issue as shown by a 2016 FireEye study [66] which found that out of 1552 vulnerabilities examined over the course of 15 years, 33% had no vendor fix at the time of public disclosure. Another recent ICS vulnerability study, by Andreeva et al. [417], found that patches were available for 85% of publicly disclosed vulnerabilities, leaving the rest with either no or partial patches.

In absence of a single, coherent patch management solution patches end up getting pushed down the supply chain on an individual or batch basis. For example, when a vulnerability is discovered in an embedded operating system, the OS vendor creates a patch and announces its availability via an update feed. It is then up to any customers such as *original equipment manufacturers* (OEMs) or *original device manufacturers* (ODMs) to monitor this feed, apply patches to their products, rebuild their firmware images and distribute them to their own customers. The further removed the party responsible for creating the patch is from the end-user of an affected product, the more complicated and slower this process becomes.

Partially as a result of this situation, many embedded systems don't even have a **secure updating mechanism** to apply patches. While there are over-the-air software updating solutions for Linux-based embedded devices [207] and firmware updating mechanisms for specific MCUs [11, 416], these are far from universally deployable. When it comes to finally applying a patch, responsibility is not always clear either. Many embedded systems don't have a real system administrator (eg. who is responsible for patching building automation systems or smart locks?) or have the end-user/owner as a potential adversary (eg. set-top

boxes) and many embedded devices vendors don't consider the products they sell to require maintenance, especially if they're disposable consumer electronics. Those vendors offering repair and replacement services, as part of a warranty or otherwise, expect to do this only in case of field defects. Some vendors try to solve this problem by offering remote maintenance services but these can become a security concern themselves as an external avenue of attack [125] or through the introduction of backdoors [83, 195, 201].

- 2. Availability Issues: Another concern is that many embedded systems are engineered for high availability. Industrial control or avionics systems, for example, have high uptime and responsiveness requirements which translate to small maintenance windows. When a system lacks hot-patching capabilities or a patch must be applied to any part of the system that requires downtime, this means patches will get applied only very infrequently.

- 3. Safety Issues: Some systems have clear risks associated with failure: eg. avionics, automotive and ICS failures can result in serious equipment damage, personal injuries or even loss of life. As a result, such *safety-critical* systems are designed and built using safety engineering [374] techniques such as failure mode and effects analysis (FMEA), fault tree analysis (FTA) and probabilistic risk assessment (PBA). These techniques seek to assess and minimize the risk of system failures and provide (different degrees of) reliability. Apart from careful coding, reviewing and verification some approaches include generating code from specifications using a certified production system or using formal methods to prove a piece of code meets certain requirements. Many embedded industries have also developed rigorous qualification and certification procedures such as D0-178B for avionics, ISO 26262 for automotive, IEC 62304 for medical and IEC 61513 for nuclear.

The issue for embedded patching here arises [420, 423] from the fact that the introduction of changes in such systems requires **recertification**. Re-certification often applies to the entire system rather than the modified components alone, especially in **mixed criticality** systems where safety- or security-critical components exist next to less critical ones, eg. infotainment systems in airplanes or cars. Since this is a costly and time-consuming process a common strategy employed to minimize re-certification cost is to delay changes until major upgrades and re-certify in bulk, but such a strategy is incompatible with the need for timely application of vulnerability patches.

The above patching issues contribute to long *vulnerability exposure* windows. The window of exposure of a given system to a particular vulnerability covers the entire period from the vulnerability's first discovery to the system being patched. The size of this window is determined by a) the time between *vulnerability discovery* and *vendor* awareness, b) the time between *vendor awareness* and *patch creation* and c) the time between *patch creation* and *patch application*.

Various factors play a role here such as how often the vulnerability is rediscovered (bug collision rate) and whether any of those parties notify the vendor, how often the vulnerability is exploited in the wild and whether the vendor is alerted in this manner, the length of the distribution chain between patch creator and applier, the regularity of updates, etc. On top of that embedded devices tend to have long life-spans which sometimes exceed the vendor support period and result in so-called 'forever days' [84] which remain unpatched forever.

As a result embedded exploits tend to have a long *shelf life* (ie. remain usable against a large number of active systems) and a correspondingly high *return on investment (ROI)* for the attacker. While there are, as of writing, no studies dealing specifically with embedded exploits in this regard, research into exploit shelf life for (mainly) general purpose systems indicates this can span years. A 2012 study by Bilge et al. [386] found that zero-day attacks, ie. the period of active exploitation of a vulnerability, lasted 312 days on average. A 2017 RAND study [388] found zero-day exploits to live 6.9 years on average and have a median survival time of 5.07 years. Given the above discussed problems with embedded patch management, it seems fair to conclude that those figures are even higher for embedded exploits.

#### 2.4 MEMORY CORRUPTION VULNERABILITIES

**Binary security**, the subject on which this work focuses, is a shorthand for all things related to *memory corruption vulnerabilities*. Memory corruption vulnerabilities [390, 459] are one of the oldest and most widely exploited classes of vulnerabilities in computer systems and arise from the use of so-called *unsafe languages*. As various studies have shown [88, 240–242], unsafe languages dominate the embedded world with between 60% and 66% of embedded projects written in C for the period 2011-2015 [242] compared to 71% in 2017 [88] and between 19% and 22% written in C++ for the period 2011-2015 [242] compared to 22% in 2017 [88].

And while strict programming guidelines and development practices can help reduce the number of bugs that end up in shipped code, some will inevitably slip under the radar as evidenced by mem-

ory corruption issues causing unintended acceleration problems in the Toyota Camry [14] and Audi 5000 [15] vehicles and miscalculation issues in the Patriot missile defense system [16], all with lethal consequences. So it should come as no surprise that some of the memory corruption bugs that end up in shipped embedded code are exploitable vulnerabilities. In fact, memory corruption issues consistently rank among the most prevalent vulnerability classes in embedded systems [49, 97, 98] with a 2016 Kaspersky study of ICS vulnerabilities even identifying them as the biggest single vulnerability class affecting industrial control systems [417].

#### 2.4.1 Language Safety

Before we discuss memory corruption exploitation, let us first briefly get at the root of the problem by looking at language safety. What precisely constitutes a 'safe' language [180] (and to what degree it is safe) is a subject of some debate but generally speaking, it comes down to ensuring programs have precise and clearly defined semantics by providing memory safety and type safety. A safe language is obliged to detect or prevent unsafe behavior either at compile-time, run-time or a combination thereof and ensure that a safety violation always results in precisely defined error behavior such as throwing an exception. A language is said to be memory safe if and only if programs written in it are "guaranteed to only access memory locations that they are permitted to access" [180] and thus detect or prevent memoryunsafe behavior such as pointer arithmetic, unbounded memory access or unconstrained casting. A language is said to be type safe if it "guarantee[s] that executing well-typed programs can never result in type errors" [180]. Examples of unsafe languages are C(++) or assembly while examples of safe langues are Ada, Erlang or (to a lesser extent) Java or C#. Safe languages are not completely fail-safe, however, seeing as how their execution might rely on an interpreter or virtual machine which itself is written in an unsafe language or might have bugs in the type checker or compiler.

As mentioned earlier unsafe languages dominate the embedded world, but not exclusively. Ada and Rust, discussed among related work in Section 10.2, are two examples of safe languages with respectively a long track record and a promising future of embedded usage. However, despite the availability of such languages there are many reasons [88, 213, 420] for the continued dominance of C(++) in the embedded world:

• **Portability**: There is a C(++) toolchain for nearly every platform and operating system and many proprietary chips only come with a vendor-supplied C toolchain. If a given embedded

project is to be portable across different platforms and operating systems, then C(++) tends to be the best choice.

- Functionality: The 'close to metal' nature of languages like C and the (safety breaking) ability to perform operations like pointer arithmetic make it well suited for the kind of optimized, low-level programming required for embedded systems.

- Overhead: As a result of language safety mechanisms, performance overheads resulting from run-time checks or lack of optimization due to compile-time checks might become unacceptable for a given embedded system.

- Maturity: C and C++ are mature languages with a long history of usage in the embedded world. As such there are many integrated development environments (IDEs), frameworks and libraries to draw upon which shortens development time.

- Legacy Code: There are billions of lines of legacy code written in C(++), many of which are reused in subsequent projects [242]. Porting these to a safe language (or the other way around), even if aided by automated tools, is a complicated, costly and messy affair [116] given issues with (re)verification of code, changed performance, timing and memory usage characteristics, switching to new development environments and the fact that programmers will possibly have to be re-trained in the new language. In many scenarios there simply won't be a strong business case for doing this.

#### 2.4.2 'Weird Machines' & Exploitation

Some memory corruption bugs are vulnerabilities which could be leveraged by an attacker to maliciously subvert the system, for example by leaking sensitive information, escalating privileges, inducing undesirable behavior or executing arbitrary code. It should be noted that not all memory corruption bugs are vulnerabilities and not all vulnerabilities are exploitable. On the other hand, the status of a bug as vulnerability or a vulnerability as exploitable is not static either. A vulnerability occurring in one place in the program code might be unexploitable while it might be exploitable in another, and a bug that is unexploitable today might become exploitable tomorrow as a result of changes in the code base (eg. components being added or removed, control-flow paths changed, modifications to system design, etc.) and vice versa.

The exploitation of memory corruption vulnerabilities often tends to be perceived more as an arcane craft based on hazy folklore than as an exact science, a view strengthened by both the target-dependent nature of many exploits and the changes in approach as a result of the 'mitigation-bypass-counter-mitigation' cat and mouse game. But exploit development has a workflow not completely unlike that of regular software engineering [435] where the exploit developer identifies computational structures in the target that allow them to manipulate the program state on the basis of inputs and distills from these structures so-called 'exploit primitives' (eg. memory read and write operations). The exploit developer then combines these inputs and exploit primitives into an exploit that achieves the desired manipulation of the program state.

A more formalized approach to reasoning about exploits comes in the form of the concept of so-called 'weird machines' [53, 54, 435–437], which can be summarized as the view that "the crafted inputs that constitute the exploit drive an input-accepting automaton already implicitly present in the target's input-handling implementation, its sets of states and transitions owing to the target's features, bugs or combinations thereof" [437]. A less concise but perhaps more intuitive way to think about weird machines is to think of 'weird states' as states falling outside of a program's 'Intended Finite State Machine (IFSM)' [54]. Certain bugs allow the attacker to enter a weird state and from there potentially transition into other weird states by means of exploit primitives, leading to a 'state space explosion' of unintended weird states. Exploits can then be understood as "programs for these 'weird machines' and serve as constructive proofs that a computation considered impossible could actually be performed by the targeted environment" [435].

#### 2.5 EXPLOIT MITIGATIONS

If we think of exploitation as the programming of weird machines through the composition of individual exploit primitives into a single 'exploit chain' it becomes clear, as pointed out by Hawkes [91], that exploit development can be frustrated by the introduction of exploit mitigations: measures which make each link harder to forge and/or lengthen the chain. In other words, by requiring more exploit primitives on part of the attacker and by making each primitive harder to construct, attacker cost are raised and certain vulnerabilities become unexploitable altogether.

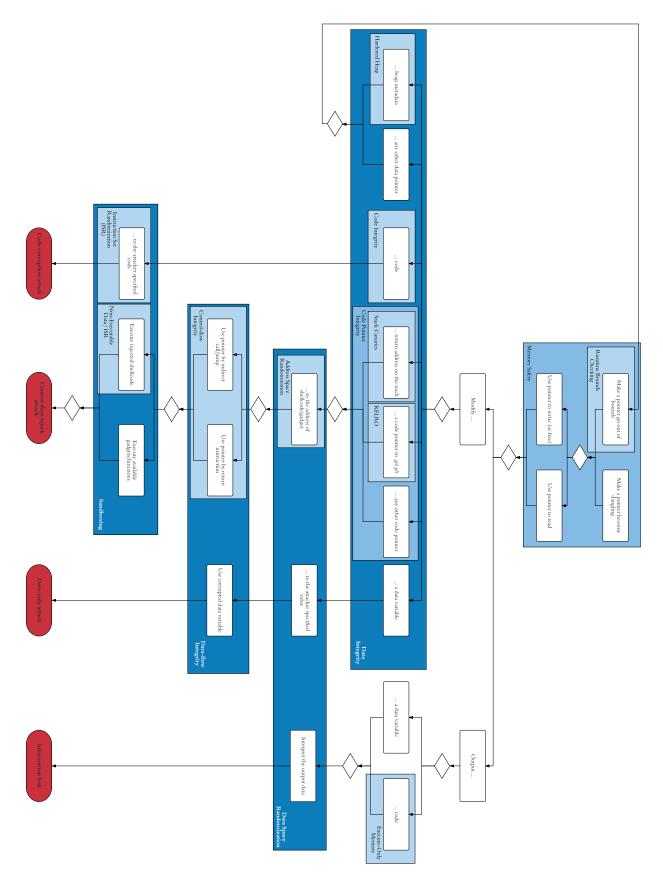

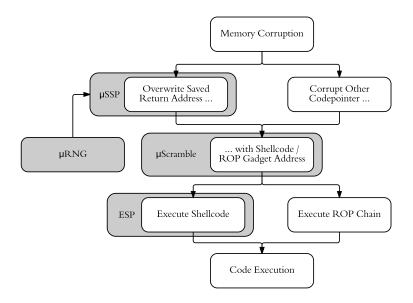

In this work, we will borrow the general model for memory corruption exploitation and proposed mitigations introduced in [390] which we slightly augmented and illustrated in Figure 2. Note that this model does not aim to be exhaustive in terms of either vulnerabilities or mitigations covered but rather represent the most popular attack and mitigations techniques occurring in literature and practice as evidenced by compiler- [25, 48, 171], OS- and 3rd party [475] sup-

port. The mitigations are listed at a conceptual level and can often be implemented in different ways of varying degrees of strength.

Since exploit mitigations target exploitation techniques rather than the root cause of vulnerabilities they are not a silver bullet [54, 61, 91]. They do, however, make exploitation more complicated and time consuming (and thus costlier) which causes the number of attackers capable of exploiting a particular vulnerability to shrink [61, 381]. Mitigations with recurring 'bypass cost' in particular act as a multiplier to exploit development time since they need to be bypassed for each bug in a chain [52]. Mitigations have been shown to cause exploit developers to shift their focus to areas not covered by mitigations [388] and as such play a key role in zero day reduction trends [250].

Developing *reliable* and *stealthy* exploits is even more challenging than developing a simple *Proof-of-Concept (PoC)*. Attackers want exploits to work on all versions and configurations of a vulnerable target and ideally without making too much 'noise' in order to prevent discovery of their attack and possible loss of their zero-day. After all as the case of the MS08-067 vulnerability [128] shows, crash log telemetry obtained via Windows Error Reporting allowed Microsoft to rapidly discover a zero-day exploit despite 95% reliability. With exploit mitigations, reliability becomes even harder to achieve as each primitive within an expanding chain will have to be reliable for the whole chain to be.

Given the above observations and the fact that more root-cause oriented solutions to memory corruption vulnerabilities in the embedded world are long-term projects at best, we consider exploit mitigations to be a viable short-term solution for increasing binary security in embedded systems. After all, as pointed out by Koopman et al. "it might make more sense to spend a small fraction of available resources providing ways to survive bugs that will inevitably be encountered, rather than throwing all resources at an attempt to achieve absolute perfection" and as such "short term research milestones should emphasize characterizing practical limitations and exploring techniques to offer near-term improvement to system builders" [423].

Figure 2: Memory corruption exploitation flowchart demonstrating mitigations at different stages based on [390]

#### EMBEDDED EXPLOIT MITIGATION BASELINE

In this chapter, we will establish a minimum exploit mitigation baseline and outline their security criteria as well as their hardware and software dependencies.

#### 3.1 ESTABLISHING A MINIMUM BASELINE

When establishing a minimum exploit mitigation baseline for embedded systems we are interested in defining an absolute minimum set of mitigations which should be reasonably expected to be present in all modern embedded systems. Because of the sheer diversity of embedded systems, we do not select our baseline on the basis of strict criteria. Instead, we only require them to be adoptable across the embedded spectrum and not rely on any specialized hardware features not commonly present in COTS embedded hardware.

Based on Figure 2, we selected the following minimum embedded exploit mitigation baseline:

- 1. Executable Space Protection (ESP) / Non-Executable Data

- 2. Address Space Layout Randomization (ASLR)

- 3. Stack Canaries

The above mitigations were selected because they are complementary and have been integrated in virtually all modern general purpose operating systems and development toolchains [48, 77, 250, 381, 388, 419], including those which are used widely in the embedded world. As such they are well understood and can reasonably be considered to be the absolute minimum in modern exploit mitigations. As noted by [355]: "when these three techniques are properly implemented on a system they provide a strong defense against most memory error exploitations".

**ESP** forces attackers to use a *code-reuse* payload which is complicated by **ASLR**'s randomization of code and data memory. **Stack canaries** prevent stack buffer overflows from overwriting the saved function return address by requiring attacker knowledge of a secret *canary value*. **ESP** and **ASLR** apply to all control-flow hijacking attacks and while **stack canaries** only protect against stack buffer overflows, these are far more common in embedded systems than they are in

modern general purpose ones [388, 417]. In addition, properly configured **ESP** (as discussed below) protects against code corruption attacks as well by making code memory non-writable. We will explain these mitigations in more depth in Section 3.2.

Baseline Limitations: Our baseline does not seek to offer exhaustive protection against all memory corruption classes and only considers control-flow hijacking and code corruption attacks while leaving data-flow and information leaks attacks unaddressed. In addition, as is usually the case with mitigations, the baseline does not guarantee absolute unexploitability of vulnerabilities but rather raises attacker cost by lengthening the exploit chain.

Keep in mind, however, that while this baseline is an absolute minimum upon which future embedded binary security work should build, embedded software has a far smaller attacker interaction surface than popular targets on general purpose machines which tends to mean that bypassing mitigations is more complicated. As pointed out by Mark Dowd [52], there have been almost no publicly known exploits achieving unconstrained code execution for Microsoft server software (eg. RPC, IIS, etc.) after the introduction of ASLR and DEP (ESP for Windows) while client software such as browsers, office suites, and PDF readers continue to be targeted by increasingly complex exploits. The key difference here is attacker control over scripting languages, multimedia elements and other interactive components which present both a larger attack surface as well as providing more granular control over the target program and memory state.

# 3.2 BASELINE MITIGATIONS IN-DEPTH

In this section we will discuss our mitigation baseline in-depth and outline the criteria for their successful implementation, because plenty can go wrong here which leads to easily bypassable mitigations.

# 3.2.1 Executable Space Protection (ESP)

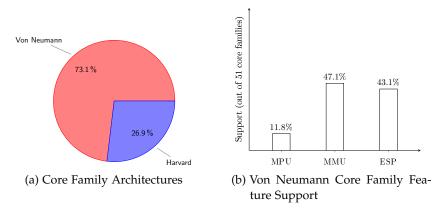

Before we can discuss the rationale behind ESP, we first need to consider the fact that there are essentially two main processor architectural style: *Harvard* and *Von Neumann*.

# Harvard and Von Neumann Architectures

The **Harvard CPU architecture** is defined as "a processor architecture that separates data and instructions into different memory spaces. The Harvard architecture is most popular on DSPs, where the benefit of simultaneous instruction and data fetches can significantly increase signal processing throughput." [402] The **Von Neumann CPU architecture** is defined as "a processor structure based on a basic theory of operation that intermixes data and instructions so that any value in memory can be executed or interpreted as data. With the exception of some supercomputers and most DSPs, the von Neumann architecture is predominant" [402].

Since in this work we are only concerned with how these architectural differences relate to memory corruption exploitation, we define a processor to have a Harvard architecture *iff* it has separate code and data memories (from the programmer's external point of view) and its data memory is non-executable. This somewhat relaxed definition allows code memory to be generally readable and sometimes writable too under limited circumstances (eg. limited to privileged instructions executed by a bootloader). All architectures which do not meet our Harvard definition are considered Von Neumann.

This architectural distinction is important when considering that an attacker executing a control-flow hijacking attack seeks to redirect intended control-flow to a piece of code of their own choosing. On a Von Neumann processor, the attacker can inject any piece of code into data memory and redirect control-flow to it to achieve arbitrary code execution. However, on a Harvard processor the attacker is restricted to repurposing fragments of pre-existing code memory by means of a so-called *code-reuse* attack.

# Code-Reuse Attacks

Code-Reuse Attacks [458] are a class of control-flow hijacking attacks where an attacker re-purposes existing code to a malicious end, thus effectively constructing a malicious payload out of pre-existing program code without having to inject a malicious payload into memory. Code-reuse attacks evolved out of the more specific Return-Into Libc (RILC) [405] attacks where whole functions are re-purposed and encompasses variants where fragments of code (often referred to as gadgets) are strung together in 'chains' such as Return-Oriented Programming (ROP) [279, 430], Jump-Oriented Programming (JOP) [458], Call-Oriented Programming (COP) [410], Sigreturn-Oriented Programming (SROP) [336] and Counterfeit Object-Oriented Programming (COOP) [339].

ROP is by far the most common and popular code-reuse attack class and there are various interactive and automated tools [111, 123, 199, 332, 469] to aid in constructing ROP chains. While ROP attacks have been shown to be Turing-complete on several platforms [337, 454], practical limitations [292] such as available gadgets, available memory or payload size restrictions mean ROP chains are often far less expressive in practice and many attackers tend to prefer 'partial ROP' [31, 279, 471] attacks where an initial ROP payload is used to change memory permissions and circumvent ESP thus allowing for injection of a second stage payload containing the actual malicious code.

**Executable Space Protection (ESP)** (also known as DEP, NX or WX memory) essentially seeks to emulate Harvard-style code and data separation on a Von Neumann processor by rendering data memory non-executable as well as usually ensuring code memory is non-writable. The goal here is to force attackers to use code-reuse attacks which are both more complicated to execute as well as often more restricted in capabilities.

ESP can be implemented either by relying on hardware support or by means of software emulation. The former case is usually implemented in the form of a dedicated hardware feature, usually part of the *Memory Management Unit (MMU)*, regulating memory executability permissions at a certain granularity level such as on a per-page basis.

64-bit PTE

Figure 3: x86 Page Table Entry (PTE) with NX bit

# Hardware ESP

We define hardware ESP support as support by a Von Neumann CPU for a feature (usually as part of integrated MPU or MMU functionality) that allows for marking memory as (non-)executable. This does not have to have been desigend or marketed explicitly as an 'ESP' feature by processor vendors for it to serve this purpose. Examples of hardware ESP features are AMD's NX bit (illustrated in Figure 3), Intel's XD bit, ARM's XN bit, MIPS' XI bit and the PowerPC segment register N bit or TLB entry EX bit.

There are multiple approaches to software-based ESP, the most well-known being the PaX project's implementation [174], the details of which are out of scope for this work. All software emulation approaches, however, incur at least some runtime overhead and tend to be architecture-specific in design.

Regardless of whether the design is hardware- or software-based, implementing ESP has an operating system component and a toolchain one. Care should be taken to meet the following criteria:

- 1. **Default Policy**: The OS components implementing ESP should have a default policy marking data memory (stack, heap, etc.) as non-executable and code memory as non-writable by default. In cases where backwards compatiblity with ESP-violating constructs (eg. dynamically generated or self-modifying code) is required, ESP policy should be enforced on an *opt-out* basis to avoid putting the burden of proper configuration on system integrators and administrators as is the case with *opt-in* policies [471].

- 2. **OS Support**: The OS memory management subsystem and program loader should ensure memory areas (eg. code memory for a loaded program, stack, and heap, etc.) are marked as per their default policy upon allocation.

3. **Toolchain Support**: The toolchain should ensure proper separation of code and data is respected by avoiding constructs which violate this (such as code trampolines, data inlined in code, etc.).

If *opt-out* support is required the toolchain should emit a marker indicating this (such as the GNU\_STACK ELF header [20]), either indicating explicit memory permissions for a given memory element overriding ESP policy or a generic *opt-out* causing a fall-back to non-ESP defaults.

- 4. **Coverage**: Shared libraries loaded by a program should fall under the program's ESP policy to prevent *'split personalities'* [208] from arising in case of *opt-out* marking conflicts.

- 5. Granularity: Care should be taken to consider the granularity level at which memory permissions are applied on a given platform to prevent ESP violations caused by overlapping or incompletely covered memory regions arising from improper alignments or data and code separation boundaries.

- 6. **Conflicting Features**: Any features which conflict with ESP policies, such as the Linux READ\_IMPLIES\_EXEC [51, 95, 152] 'legacy support' personality flag, should be turned off by default.

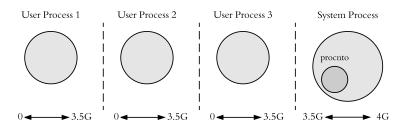

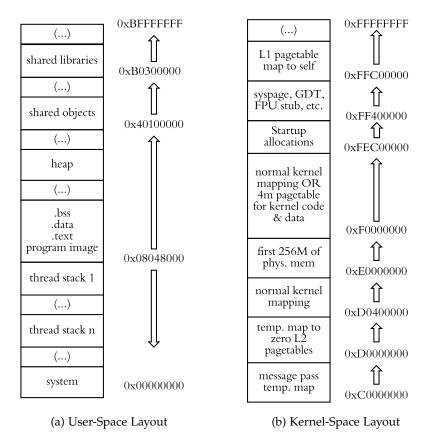

# 3.2.2 Address Space Layout Randomization (ASLR)

When developing exploits, attackers rely on knowledge of the target application's memory map for write and read targets as well as crafting code-reuse payloads. Address Space Layout Randomization (ASLR) [22, 81] is a technique which seeks to break this assumption by ensuring memory layout secrecy via randomization of addresses belonging to various memory objects (eg. code, stack, heap, etc.) and rendering them hard to guess as illustrated in Figure 4. A full overview of all existing ASLR designs and proposals is out of scope for this work but they can be categorized based on the following decisions:

- 1. When to (re)randomize: Randomization can occur at different points in time: at boot, when a program is loaded, when a thread is created, etc. This choice determines the variation in memory layout between different processes running on the same machine and the options for relocation frequency.

- 2. What to randomize: Program memory can be seen as divided into different memory objects all of which can be randomized to different degrees. In order to thwart code-reuse attacks, at least code memory (both that of the main program image and any

(c) ASLR with PIE

Figure 4: Address Space Layout Randomization (ASLR) [22]

shared libraries) needs to be randomized. Depending on the operating system design, randomization of certain memory objects might require them to be compiled in a special fashion such as *Position Independent Executables (PIE)* required for main program code randomization as illustrated in Figure 4b versus Figure 4c.

3. How to randomize: Randomization can occur at different levels of granularity (eg. only randomizing memory object base addresses vs. randomizing their internal layout) and with different degrees of correlation (eg. loading all shared libraries in-order at static offsets from the first or randomizing them individually).

It is crucial for the effectiveness of ASLR that sensitive addresses are both *secret* and *unpredictable*. Generally speaking the more granular and frequent the (re)randomization, the better.

Over the years, ASLR implementations in various operating systems have been found to suffer from a variety of weaknesses [81, 154, 359]. Based on prior work [81, 355, 356] we can conclude ASLR security is based upon the following criteria:

- 1. Entropic Quality: The probability that an attacker can guess the locations of randomized memory objects within a reasonable amount of time needs to be low for ASLR to be secure. As such we require randomized addresses to have high entropic quality, something which has three different dimensions [355]:

- a) Non-Randomized Sections: A single non-randomized (code) section can often be used by an attacker to bypass ASLR if sufficient gadgets reside within it. On Linux VDSO (named linux-gate.so on some systems) [77] used to be mapped at a fixed address while Windows used to be plagued by commonly loaded old non-ASLR libraries such as msvcr71.dll [472] or structures mapped at fixed addresses such as SharedUserData or Wow64SharedInformation [271]. In some cases, randomized memory objects might end up being mapped at fixed addresses as an unforseen side-effect of memory pressure [60]. ASLR as implemented in popular general purpose operating systems has evolved to avoid these pitfalls by carefully randomizing *all* memory objects.

- b) Range of Entropy: The range of possible values for a given randomized address determines the probability that an attacker can guess the address within a reasonable amount of time. this range is limited by the available (virtual) memory space and the flexibility of memory object placement the operating system allows.

- c) Relocation Frequency: Address randomization can occur at different points in time and either once or more frequently. Ideally, all memory objects for different processes are all mapped at different locations with respect to both previous execution runs and other processes. It is also possible to relocate memory objects during runtime so that addresses are not only randomized per execution run and per process but also randomized throughout a single run. While the latter approach is not integrated into the ASLR implementation of any major operating system and comes with serious overhead, it has the additional benefit of limiting the usefulness of information leaks.

- 2. **Brute-Force Resistance**: In addition to the entropic quality, ASLR designers need to take *memory layout inheritance* into account when seeking to harden against brute-force attacks. Many operating systems have process management models where child processes inherit the memory layout of their parents. This has two major drawbacks: a) It makes application architectures where children are respawned after crashing highly vulnerable to brute-force attacks b) Child processes know the memory layouts of sibling processes which constitutes a breach of ASLR's memory

secrecy assumption if child processes are considered independent (eg. Android's Zygote sandboxing model).

The former is particularly dangerous in the light of *byte-by-byte* brute-force attacks against ASLR [273, 356]. Here an attacker with fine-grained control over their memory corruption vector targeting an application with respawning child processes or threads starts by overwriting the first byte of a given codepointer and observes the resulting control-flow. If the target thread or child process crashes their guess was incorrect, while if it continues running as intended it was correct. Because of *memory layout inheritance*, the codepointer value does not change between guesses and the attacker can try all 256 possible values before obtaining the correct value for the first byte and move on to the next one. In this manner, the attacker only needs at most 256<sup>N</sup> trials to brute-force the target codepointer, where N is the codepointer byte-width.

- 3. Information Leaks: Since ASLR security rests on memory layout or contents (eg. in the form of code or data pointer values) can be used to defeat it. The impact of a particular information leak depends on the scope and flexibility of the leak itself as well as the ASLR implementation but generally speaking they are the most reliable way to defeat modern ASLR implementations. While information leaks might result from and require an attacker to find an additional bug on top of the one used to hijack control-flow, sufficiently flexible vulnerabilities can often be crafted into information leaks themselves. In addition, operating system designers need to consider memory layout and content as secret when introducing ASLR and ensure they are not disclosed to potential attackers by system features [238, 452].

- 4. Correlation Attacks: When the location of one memory object can be used to deduce the location of others these are said to be correlated. Correlation can either be *total*, where the attacker can obtain the exact location of a correlated memory object, or *partial*, where the attacker's search space is reduced by using correlation information. Many popular ASLR implementations suffer(ed) from some form of correlation, allowing attackers to leverage less powerful or even otherwise useless information leaks to fully defeat ASLR. An example of a *total* correlation attack is the offset2lib [355] attack affecting PIE binaries on Linux and the ASLR bypass used in the Metaphor exploit [19] for the Stagefright vulnerability.

Figure 5: Stack Canary Example

# 3.2.3 Stack Canaries

A **Stack Canary Scheme** [190] is a security mechanism that aims to protect against 'linear' stack buffer overflows. That is, stack buffer overflows that seek to overflow a local buffer into local stackframe metadata such as the saved frame pointer or return address. It does this by placing a so-called *canary* or *guard* value between the metadata and local variables. Over the years, stack canaries have evolved and have seen many incarnations in popular toolchains and operating systems [137, 190, 470] but they are generally impelemented as a compiler extension (with an operating system component) which:

- Inserts code to generate a random master canary value at program startup and store it somewhere, preferably in a location that cannot be overwritten or read without invocation of a dedicated instruction (eg. in a special data segment).

- 2. Instruments function prologs to push a copy of the master canary value to the stack between stackframe metadata and local variables, as illustrated in Figure 5.